在當(dāng)今數(shù)字時(shí)代的核心,半導(dǎo)體大規(guī)模集成電路(VLSI)作為電子設(shè)備的大腦,其性能與可靠性直接決定了從智能手機(jī)到數(shù)據(jù)中心,從自動(dòng)駕駛汽車(chē)到工業(yè)控制系統(tǒng)的方方面面。將數(shù)以?xún)|計(jì)甚至百億計(jì)的晶體管集成在一塊微小的芯片上,并確保其出廠時(shí)功能完好、性能達(dá)標(biāo),是一個(gè)極其復(fù)雜且關(guān)鍵的環(huán)節(jié)。這正是大規(guī)模集成電路測(cè)試的核心使命——它是在芯片設(shè)計(jì)與制造之后、交付給客戶之前,守護(hù)質(zhì)量與可靠性的最后一道,也是至關(guān)重要的一道防線。

一、測(cè)試的必要性與挑戰(zhàn)

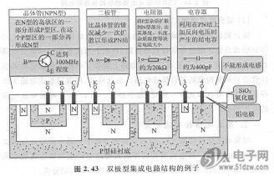

隨著工藝節(jié)點(diǎn)不斷微縮,芯片復(fù)雜度呈指數(shù)級(jí)增長(zhǎng)。制造過(guò)程中的微小缺陷,如微粒污染、金屬線短路或開(kāi)路、晶體管閾值電壓漂移等,都可能導(dǎo)致芯片功能失效或性能降級(jí)。測(cè)試的目的就是將這些有缺陷的芯片(稱(chēng)為“瑕疵品”)從大量合格品中篩選出來(lái)。其挑戰(zhàn)在于:

- 超高復(fù)雜度:如何用有限的時(shí)間和成本,對(duì)內(nèi)部狀態(tài)天文數(shù)字般的電路進(jìn)行有效驗(yàn)證?

- 物理限制:芯片的輸入/輸出引腳數(shù)量有限,難以直接觀測(cè)和控制內(nèi)部每一個(gè)節(jié)點(diǎn)。

- 故障模型多樣性:故障類(lèi)型繁多,從固定的“卡在0/1”故障,到更復(fù)雜的延時(shí)故障、橋接故障等。

- 測(cè)試成本壓力:測(cè)試成本在芯片總成本中的占比日益升高,需要在測(cè)試覆蓋率、測(cè)試時(shí)間與成本之間尋求最佳平衡。

二、測(cè)試的主要流程與類(lèi)型

集成電路測(cè)試是一個(gè)系統(tǒng)化工程,通常貫穿于設(shè)計(jì)、制造和封裝的全過(guò)程。

1. 設(shè)計(jì)階段:可測(cè)試性設(shè)計(jì)

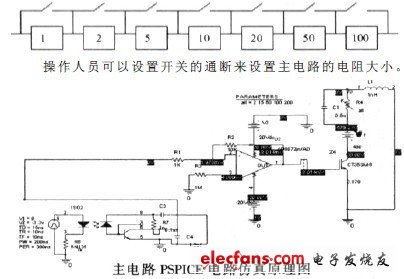

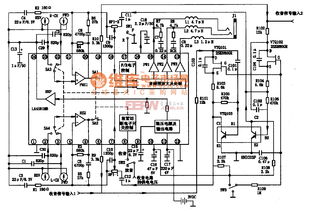

這是測(cè)試的基石。為了降低測(cè)試難度,工程師會(huì)在芯片設(shè)計(jì)時(shí)主動(dòng)插入可測(cè)試性結(jié)構(gòu),主要包括:

- 掃描鏈:將芯片內(nèi)部的時(shí)序邏輯單元(觸發(fā)器)串聯(lián)成一條或多條鏈,在測(cè)試模式下可以像移位寄存器一樣,方便地將測(cè)試向量輸入、將內(nèi)部狀態(tài)輸出,極大地提高了內(nèi)部節(jié)點(diǎn)的可控性和可觀測(cè)性。

- 內(nèi)建自測(cè)試:在芯片內(nèi)部集成專(zhuān)門(mén)的測(cè)試電路,使其能夠自行生成測(cè)試向量、執(zhí)行測(cè)試并分析結(jié)果,特別適用于對(duì)存儲(chǔ)器(如SRAM、DRAM)的測(cè)試。

- 邊界掃描:主要用于測(cè)試芯片之間電路板級(jí)的互連,通過(guò)IEEE 1149.1(JTAG)標(biāo)準(zhǔn)實(shí)現(xiàn)。

2. 制造后測(cè)試:核心檢測(cè)環(huán)節(jié)

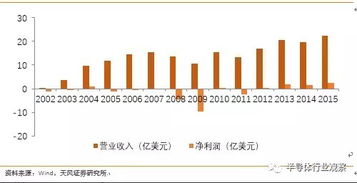

在晶圓制造完成和芯片封裝后,會(huì)使用昂貴的自動(dòng)測(cè)試設(shè)備(ATE)進(jìn)行嚴(yán)格測(cè)試。主要包括:

- 功能測(cè)試:驗(yàn)證芯片是否能夠正確執(zhí)行其設(shè)計(jì)的所有功能。通過(guò)輸入一系列功能向量,檢查輸出是否符合預(yù)期。這是最基本的測(cè)試。

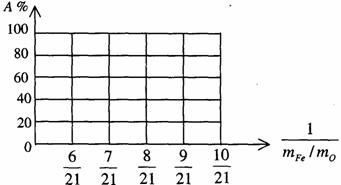

- 參數(shù)測(cè)試:驗(yàn)證芯片的電氣參數(shù)是否達(dá)標(biāo),如供電電流、輸入輸出電壓/電流、信號(hào)傳輸延時(shí)、功耗等。這關(guān)系到芯片的性能和可靠性。

- 結(jié)構(gòu)測(cè)試:不關(guān)心具體功能,而是基于故障模型,檢測(cè)制造中可能引入的物理缺陷。通過(guò)向掃描鏈加載測(cè)試向量,可以高效地檢測(cè)固定型故障。

- 硅片調(diào)試與特性測(cè)試:對(duì)初批芯片進(jìn)行深入分析,驗(yàn)證其在各種電壓、溫度角況下的性能極限,為產(chǎn)品標(biāo)定提供依據(jù)。

三、前沿發(fā)展與未來(lái)趨勢(shì)

面對(duì)先進(jìn)工藝(如5納米、3納米)和新型架構(gòu)(如Chiplet、3D集成)帶來(lái)的新挑戰(zhàn),測(cè)試技術(shù)也在不斷演進(jìn):

- 基于人工智能的測(cè)試優(yōu)化:利用機(jī)器學(xué)習(xí)算法優(yōu)化測(cè)試向量生成,減少測(cè)試集規(guī)模,提升故障覆蓋率,并預(yù)測(cè)芯片缺陷。

- 面向系統(tǒng)級(jí)芯片的測(cè)試:對(duì)于集成CPU、GPU、AI加速器、多種IO的復(fù)雜SoC,需要協(xié)同的層次化測(cè)試策略和更高效的測(cè)試訪問(wèn)機(jī)制。

- 可靠性測(cè)試與預(yù)測(cè):不僅關(guān)注出廠時(shí)的好壞,更關(guān)注芯片在整個(gè)生命周期內(nèi)的可靠性,如對(duì)老化、軟錯(cuò)誤、熱效應(yīng)的測(cè)試與監(jiān)控。

- 測(cè)試安全:防止測(cè)試接口成為黑客攻擊的后門(mén),確保測(cè)試基礎(chǔ)設(shè)施的安全。

###

半導(dǎo)體大規(guī)模集成電路的測(cè)試,遠(yuǎn)非簡(jiǎn)單的“好壞篩選”。它是一個(gè)融合了電路設(shè)計(jì)、計(jì)算機(jī)科學(xué)、概率統(tǒng)計(jì)和精密工程的深度技術(shù)領(lǐng)域。正是這些看不見(jiàn)的、嚴(yán)謹(jǐn)而復(fù)雜的測(cè)試流程,確保了每一顆投入市場(chǎng)的芯片都能穩(wěn)定、可靠地運(yùn)行,從而支撐起我們高度數(shù)字化的世界。隨著芯片繼續(xù)朝著更復(fù)雜、更集成的方向發(fā)展,測(cè)試技術(shù)作為產(chǎn)業(yè)背后的“質(zhì)量守門(mén)員”,其重要性只會(huì)與日俱增。