集成電路芯片,作為現代電子設備的心臟,其成本構成遠比表面看到的硅片價格復雜。從一粒沙子到一枚功能強大的芯片,其成本涵蓋了設計、制造、封裝測試以及知識產權等多個維度。理解這些成本要素,有助于我們洞察半導體產業的定價邏輯與技術壁壘。

一、設計與研發成本:高昂的“智力”投入

芯片的成本首先源于其設計與研發。這是一個資金與技術密集的先行階段,成本極高且具有高風險性。

- 人力成本:一支由架構師、設計工程師、驗證工程師等組成的頂尖團隊,其薪酬是主要開支。

- EDA工具授權費:芯片設計必須使用昂貴的電子設計自動化(EDA)軟件,其年度授權費用動輒數百萬甚至上千萬美元。

- IP授權費:為了縮短設計周期,設計公司常需購買成熟的IP核(如ARM處理器核心、接口協議等),這也是一筆不菲的固定支出。

- 流片(Tape-out)費用:設計完成后,需要交付晶圓廠進行首次試生產以驗證設計,單次流片費用可能高達數百萬至數千萬美元,且不保證成功。

這部分成本需要分攤到最終成功量產并銷售的所有芯片中。芯片越復雜、工藝越先進,設計和研發成本就越是呈指數級增長。一款先進制程的高端處理器,其研發投入可達數十億美金。

二、制造成本:核心的“物理”開銷

制造是在晶圓廠(Fab)完成的環節,其成本主要由以下幾部分構成:

- 晶圓成本:即硅片本身的材料成本,晶圓尺寸越大(如12英寸對比8英寸),單位成本效益通常越高。

- 工藝制程成本:這是制造的核心成本。工藝越先進(如5納米、3納米),所需的光刻、刻蝕、離子注入等設備越昂貴,工藝流程也越復雜,導致每片晶圓的加工成本急劇上升。光刻機(如EUV)單臺售價就超過1億美元。

- 良率(Yield):并非所有在晶圓上制造出來的芯片都是可用的。良率是指合格芯片所占的比例。良率越低,意味著每個功能完好芯片所分攤的制造成本就越高。提升良率是晶圓廠的核心競爭力之一。

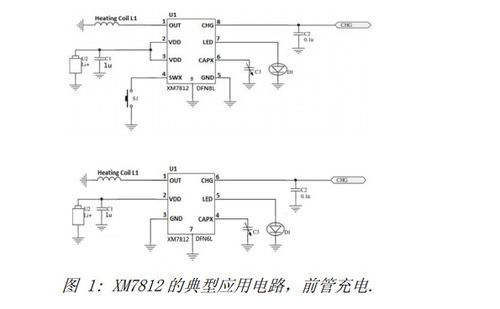

單個芯片的晶圓制造成本可以粗略用以下公式估算:

芯片成本 ≈ 晶圓價格 / (每片晶圓產出的芯片數量 × 良率)

其中,每片晶圓產出的芯片數量取決于芯片尺寸(Die Size)和晶圓尺寸。

三、封裝與測試成本:最后的“包裝”與“質檢”

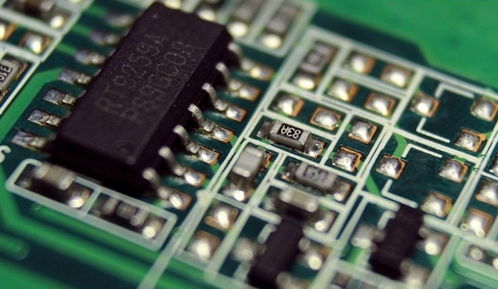

從晶圓上切割下來的裸片(Die),必須經過封裝和測試才能成為可銷售的芯片。

- 封裝成本:將裸片封裝在保護性外殼中,并引出連接引腳。封裝形式多樣(如QFN、BGA、CSP等),越復雜、集成度越高的封裝(如先進封裝、3D封裝),成本也越高。

- 測試成本:對封裝后的芯片進行功能和性能測試,篩選出合格品。測試設備昂貴,測試程序開發與測試時間也構成成本。

四、其他重要成本因素

1. 知識產權與專利:芯片可能涉及的專利許可費用。

2. 營銷與銷售成本:市場推廣、渠道建設等費用。

3. 固定資產折舊:晶圓廠和封測廠的巨額建設投資(一座先進晶圓廠造價可達百億美金)需要按年限折舊,分攤到每片晶圓或每個芯片上。

4. 規模效應:當芯片產量巨大時,高昂的前期設計、研發及設備折舊成本被極大攤薄,導致單顆芯片成本顯著下降。這正是很多消費級芯片在生命周期后期價格走低的原因。

****

集成電路芯片的成本是一個多層次的復合體。對于先進的高性能芯片(如CPU、GPU),設計和研發成本主導了總成本;而對于成熟制程的量大面廣芯片(如某些MCU、電源管理芯片),制造成本和封裝測試成本占比更大。芯片的最終價格,則由其總成本、市場供需關系、競爭格局以及廠商的戰略定位共同決定。理解這些成本構成,不僅能看懂芯片定價,更能深刻理解半導體行業技術密集、資本密集、高度依賴規模經濟的本質特性。